# 5-Port 10/100/1000 Smart Ethernet Switch

### Features

- Stand Alone Switch On A Chip

- 5 Ethernet 10/100/1000 ports

- I Ethernet 10/100 port

- MII/GMII interface for 5 ports

- I extra MII interface for 6<sup>th</sup> port

- Four Classes of Service (CoS) selectable for each port and/or checked via IP Header and 802.1Q VLAN Tag

- Five port-based VLANs

- Maximum throughput, non head-of-line blocking architecture

- Embedded SSRAM packet buffer/address table

- 8K MAC address table

- Each port is configurable to 10 full/half duplex, 100 full/half duplex and 1000 full duplex mode

- Flow-control ability is able to set for both full and half duplex mode

- Broadcast throttling

- Port Mirroring

- Serial EEPROM Interface, EEPROM is optional

- MDIO master for PHY configuration / polling

- 0.18 micron technology

- 2V and 3.3V dual voltage power supply

- Packaged in PBGA 292

- 25MHz crystal input only

#### **General Description**

TC9205M is a fully integrated 5 Port 10/100/1000 smart Ethernet switch controller designed for low cost and high performance solutions. The chip embeds necessary SSRAM for packet buffering and MAC address table. It provides MII / GMII / interface for all ports.

A store-and-forward switching method using a non-blocking architecture is implemented within TC9205M to improve the availability and bandwidth. The chip embeds packet buffer, which it supports normal and priority queues for each transmission port.

TC9205M provides evolved CoS with four levels of priority. The priority can be checked via layer 2 (802.1Q VLAN Tagging) and/or layer 3 (IP Header TOS bits) packets. Port based priority is also provided to ensure transmission with precedence for all packets incoming from selected port(s). This feature allows improved support for multimedia applications.

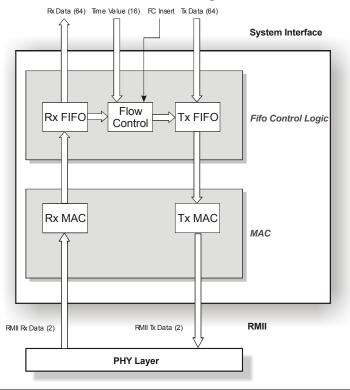

The chip embeds IEEE 802.3 MAC functions for each port and these functions support full and half duplex modes for both 10 and 100 Mbits/s data rates and full duplex for 1000 Mbit/s. Each port includes dedicated receive and transmit FIFOs with necessary logic to implement flow control for both full and half duplex modes. TC9205M uses IEEE 802.3x frame based flow control for full duplex and backpressure for half duplex.

TC9205M handles an 8K address-lookup table with searching, self-learning, and automatic aging, at very high speed and excellent address space coverage. Forwarding rules are implemented according to IEEE 802.1D specifications. Filtering capabilities for bad packets and packets with Reserved Group Address DA are also provided.

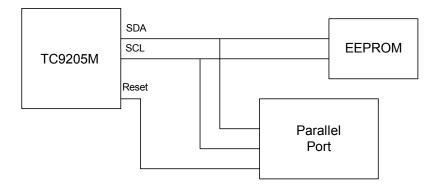

The pin configuration interface comprises 40 configurations, which are shared with GMII output pins by latching the configuration data during reset. An external EEPROM device can also be used to configure the TC9205M at power-up. With reference to pin configuration interface, the EEPROM extends the chip's configuration capability with new features and enables a jumper-less configuration mode using a parallel interface for reprogramming. A virtual internal EEPROM mode is also provided to enable the use of the programming interface in the absence of external EEPROM. TC9205M can make effective use by most of its features using only the pin configuration interface.

TC9205M includes a physical layer configuration / polling entity, which it is use to configure the phy functions and to monitor the physical layer transceiver's speed, duplex mode, link status and full duplex flow control ability for each port. The chip provides four modes for phy configurations, which these modes include auto-negotiation disable procedure for 10/100 speed modes. The phy configuration information is stored in EEPROM setting.

The chip requires a 25 MHz system clock, dual 2V and 3.3V power supply and is packaged in PBGA 292.

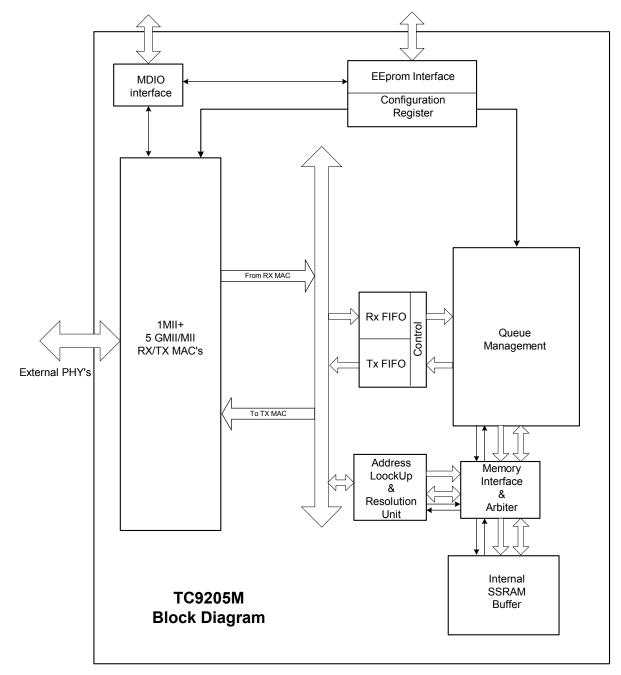

# **Block Diagram**

# **Table Of Contents**

|         | eatures1                                                             |    |  |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------|----|--|--|--|--|--|--|--|

| Ger     | eneral Description1                                                  |    |  |  |  |  |  |  |  |

| Bloo    | Block Diagram                                                        |    |  |  |  |  |  |  |  |

| Tab     | Table Of Contents                                                    |    |  |  |  |  |  |  |  |

| Rev     | Revision History                                                     |    |  |  |  |  |  |  |  |

|         | Pins Placement                                                       |    |  |  |  |  |  |  |  |

| 1       | Pin Listing (PBGA 292)                                               |    |  |  |  |  |  |  |  |

| 2       | Ethernet Media Access Controller                                     |    |  |  |  |  |  |  |  |

|         | 2.1 Receive MAC                                                      |    |  |  |  |  |  |  |  |

|         | 2.2 Transmit MAC                                                     |    |  |  |  |  |  |  |  |

| 3       | MAC Address Handling                                                 |    |  |  |  |  |  |  |  |

| 4       | Queue Management                                                     |    |  |  |  |  |  |  |  |

| 5       | Classes of Service                                                   |    |  |  |  |  |  |  |  |

| 6       | Flow Control                                                         |    |  |  |  |  |  |  |  |

| 7       | Broadcast Throttling                                                 |    |  |  |  |  |  |  |  |

| 8       | Port Mirroring                                                       |    |  |  |  |  |  |  |  |

| 9       | Physical Layer Configuration / Polling                               |    |  |  |  |  |  |  |  |

| 3<br>10 | EEPROM Interface                                                     |    |  |  |  |  |  |  |  |

| 10      | 10.1 Reprogramming the EEPROM for reconfiguration                    |    |  |  |  |  |  |  |  |

|         |                                                                      |    |  |  |  |  |  |  |  |

|         |                                                                      |    |  |  |  |  |  |  |  |

|         | 10.3 Register Description                                            |    |  |  |  |  |  |  |  |

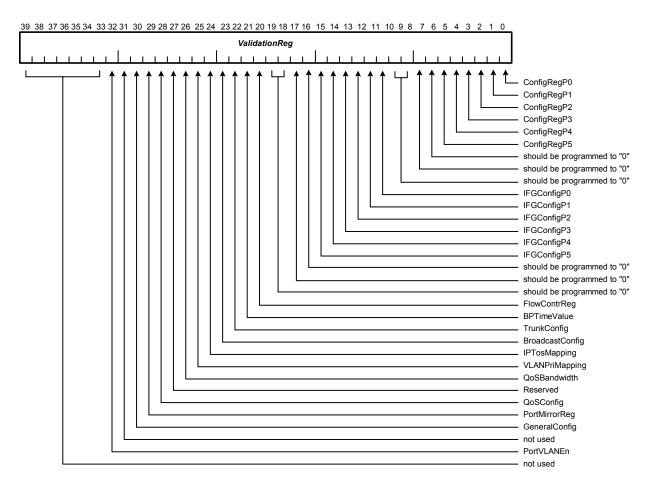

|         | 10.3.1 Validation Register                                           |    |  |  |  |  |  |  |  |

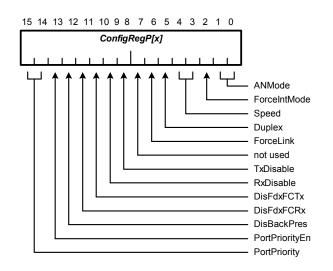

|         | 10.3.2 Port [X] Configuration Register                               |    |  |  |  |  |  |  |  |

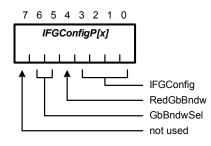

|         | 10.3.3 Port [X] IFG Configuration Register                           |    |  |  |  |  |  |  |  |

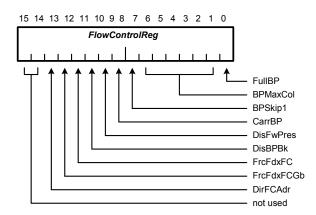

|         | 10.3.4 Flow Control Register                                         |    |  |  |  |  |  |  |  |

|         | 10.3.5 Backpressure Time Value Register                              |    |  |  |  |  |  |  |  |

|         | 10.3.6 Flow Control Port Base Address Register                       |    |  |  |  |  |  |  |  |

|         | 10.3.7 Reserved                                                      |    |  |  |  |  |  |  |  |

|         | 10.3.8 Broadcast Configuration Register                              |    |  |  |  |  |  |  |  |

|         | 10.3.9 IP Priority Mapping Register                                  |    |  |  |  |  |  |  |  |

|         | 10.3.10 VLAN Priority Mapping Register                               |    |  |  |  |  |  |  |  |

|         | 10.3.11 CoS Bandwidth Register                                       |    |  |  |  |  |  |  |  |

|         | 10.3.12 Reserved Register                                            |    |  |  |  |  |  |  |  |

|         | 10.3.13 CoS Configuration Register                                   |    |  |  |  |  |  |  |  |

|         | 10.3.14 Port Mirroring Register                                      |    |  |  |  |  |  |  |  |

|         | 10.3.15 General Configuration Register                               |    |  |  |  |  |  |  |  |

|         | 10.3.16 Port VLAN Enable Register                                    |    |  |  |  |  |  |  |  |

|         | 10.3.17 VLAN [Y] Register                                            | 43 |  |  |  |  |  |  |  |

|         | 10.4 Writing / Reading PHY management registers via EEPROM interface | 44 |  |  |  |  |  |  |  |

|         | 10.4.1 Data Write Register                                           | 44 |  |  |  |  |  |  |  |

|         | 10.4.2 Physical Layer Device Address Register                        |    |  |  |  |  |  |  |  |

|         | 10.4.3 Physical Layer's Register Address Register                    | 45 |  |  |  |  |  |  |  |

|         | 10.4.4 IO Status Control Register                                    |    |  |  |  |  |  |  |  |

|         | 10.4.5 Data Read Register                                            | 46 |  |  |  |  |  |  |  |

| 11      | Timing Requirements                                                  |    |  |  |  |  |  |  |  |

|         | 11.1 GMII / MII Receive Timing Requirements                          | 47 |  |  |  |  |  |  |  |

|         | 11.2 GMII / MII Transmit Timing                                      |    |  |  |  |  |  |  |  |

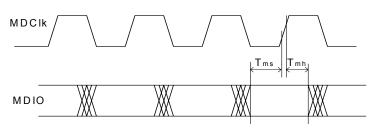

|         | 11.3 PHY Management (MDIO) Timing                                    | 48 |  |  |  |  |  |  |  |

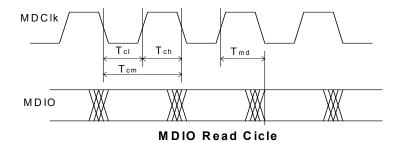

|         | 11.4 EEPROM Timing                                                   |    |  |  |  |  |  |  |  |

| 12      | Electrical Specifications                                            |    |  |  |  |  |  |  |  |

|         | 12.1 ABSOLUTE MAXIMUM RATINGS                                        | 50 |  |  |  |  |  |  |  |

|    | 12.2  | RECOMMENDED OPERATING CONDITIONS | 50  |

|----|-------|----------------------------------|-----|

|    | 12.3  | DC CHARACTERISTICS               | 50  |

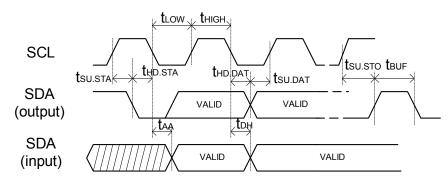

| 13 | Packa | ge Detail                        | .51 |

# **Revision History**

| Revision #    | Change Description                                                                                                                                                                                   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TC9205-DS-R02 |                                                                                                                                                                                                      |

| TC9205-DS-R03 | <ol> <li>Modify "Pin Latched" field in Class of Service section.</li> <li>Correct the register map of "Broadcast Configuration Register"</li> <li>Correct the junction temperature limit.</li> </ol> |

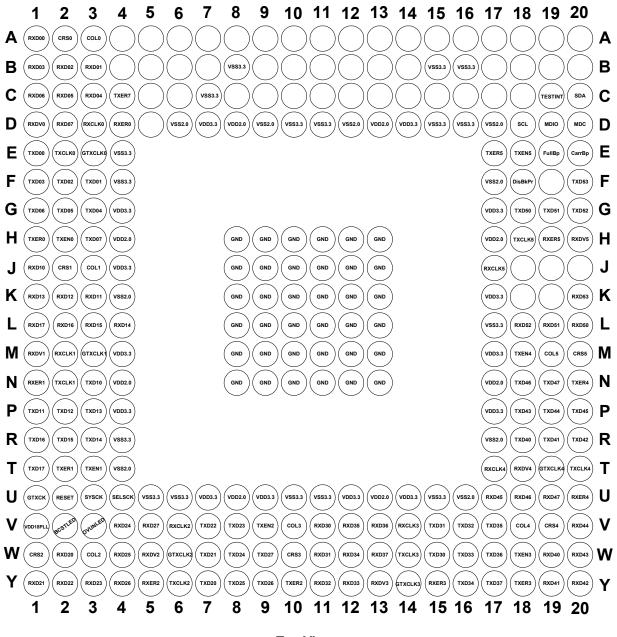

**Pins Placement**

Top View

# 1 Pin Listing (PBGA 292)

- $I \Rightarrow digital input$

- $I_s \implies$  schmitt trigger digital input

- $I_{pd} \Rightarrow$  digital input with internal pull down

- $I/O \Rightarrow$  digital bi-directional

- $I/O_{pd} \Rightarrow digital bi-directional with internal pull down$

- $I/O_{pu} \Rightarrow$  digital bi-directional with internal pull up

- $O \Rightarrow digital output$

- $P \Rightarrow power$

- $G \Rightarrow ground$

| No. | Pin label   | Туре              | Description                                                                                                                                                                                                                                                                                                              |

|-----|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G4  | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                       |

| E4  | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                   |

| J4  | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                       |

| F4  | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                   |

| B15 | Vss 3.3     | Р                 |                                                                                                                                                                                                                                                                                                                          |

| H4  | Vdd 2.0     | Р                 | Digital +2.0V power supply for core                                                                                                                                                                                                                                                                                      |

| B16 | Vss 3.3     | Р                 |                                                                                                                                                                                                                                                                                                                          |

| K4  | Vss 2.0     | G                 | Digital ground for core                                                                                                                                                                                                                                                                                                  |

| M4  | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                       |

| R4  | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                   |

| N4  | Vdd 2.0     | Р                 | Digital +2.0V power supply for core                                                                                                                                                                                                                                                                                      |

| T4  | Vss 2.0     | G                 | Digital ground for core                                                                                                                                                                                                                                                                                                  |

| P4  | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                       |

| C7  | Vss 3.3     | Р                 |                                                                                                                                                                                                                                                                                                                          |

| U5  | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                   |

| B8  | Vss 3.3     | Р                 |                                                                                                                                                                                                                                                                                                                          |

| U7  | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                       |

| U6  | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                   |

| U9  | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                       |

| H3  | TxData0_7   | 0                 | GMII transmit data - bits 7                                                                                                                                                                                                                                                                                              |

| G1  | TxData0_6   | 0                 | GMII transmit data - bits 6                                                                                                                                                                                                                                                                                              |

| G2  | TxData0_5   | 0                 | GMII transmit data - bits 5                                                                                                                                                                                                                                                                                              |

| U10 | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                   |

| G3  | TxData0_4   | 0                 | GMII transmit data - bits 4                                                                                                                                                                                                                                                                                              |

| F1  | TxData0_3   | 0                 | GMII/MII transmit data - bits 3                                                                                                                                                                                                                                                                                          |

| F2  | TxData0_2   | 0                 | GMII/MII transmit data - bits 2                                                                                                                                                                                                                                                                                          |

| U12 | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                       |

| F3  | TxData0_1   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 1                                                                                                                                                                                                                                                                                           |

|     | PriClass0_1 |                   | Priority class - most significant bit.                                                                                                                                                                                                                                                                                   |

| E1  | TxData0_0   | I/O <sub>pu</sub> | GMII/MII transmit data - least significant bit                                                                                                                                                                                                                                                                           |

|     | PriClass0_0 |                   | Priority class - least significant bit. Sets priority level per port basis.<br>PriClass[0] - '00' - port 0 has low priority<br>PriClass[0] - '01' - port 0 has normal priority<br>PriClass[0] - '10' - port 0 has high priority<br>PriClass[0] - '11' - port 0 has very high priority<br>PriClass[0] is latched on reset |

| H2  | TxEn0       | 0                 | GMII/MII transmit enable                                                                                                                                                                                                                                                                                                 |

| No. | Pin label   | Туре              | Description                                                                                                                                                                                                                                                                                                          |

|-----|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E3  | GTxClk0     | 0                 | GMII transmit clock                                                                                                                                                                                                                                                                                                  |

| U11 | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                               |

| H1  | TxEr0       | I/O <sub>pd</sub> | Transmit Error                                                                                                                                                                                                                                                                                                       |

| E2  | TxClk0      |                   | MII transmit clock                                                                                                                                                                                                                                                                                                   |

| A2  | Crs0        | I <sub>s</sub>    | MII carrier sense indication                                                                                                                                                                                                                                                                                         |

| A3  | Col0        | I <sub>s</sub>    | MII collision indication                                                                                                                                                                                                                                                                                             |

| D4  | RxEr0       | I <sub>s</sub>    | Receive Error                                                                                                                                                                                                                                                                                                        |

| U8  | Vdd 2.0     | Р                 | Digital +2.0V power supply for core                                                                                                                                                                                                                                                                                  |

| D3  | RxClk0      | Ι                 | MII receive clock                                                                                                                                                                                                                                                                                                    |

| D1  | RxDv0       | I <sub>s</sub>    | GMII/MII data valid                                                                                                                                                                                                                                                                                                  |

| A1  | RxData0_0   | ا <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                    |

| B3  | RxData0_1   | ا <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                    |

| B2  | RxData0_2   | ا <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                    |

| U16 | Vss 2.0     | G                 | Digital ground for core                                                                                                                                                                                                                                                                                              |

| B1  | RxData0_3   | ا <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                    |

| C3  | RxData0_4   | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                          |

| C2  | RxData0_5   | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                          |

| C1  | RxData0_6   | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                          |

| D2  | RxData0_7   | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                          |

| U14 | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                   |

| U15 | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                               |

| T1  | TxData1_7   | 0                 | GMII transmit data - bits 7                                                                                                                                                                                                                                                                                          |

| R1  | TxData1_6   | 0                 | GMII transmit data - bits 6                                                                                                                                                                                                                                                                                          |

| R2  | TxData1_5   | 0                 | GMII transmit data - bits 5                                                                                                                                                                                                                                                                                          |

| U13 | Vdd 2.0     | Р                 | Digital +2.0V power supply for core                                                                                                                                                                                                                                                                                  |

| R3  | TxData1_4   | 0                 | GMII transmit data - bits 4                                                                                                                                                                                                                                                                                          |

| P3  | TxData1_3   | 0                 | GMII/MII transmit data - bits 3                                                                                                                                                                                                                                                                                      |

| P2  | TxData1_2   | 0                 | GMII/MII transmit data - bits 2                                                                                                                                                                                                                                                                                      |

| R17 | Vss 2.0     | G                 | Digital ground for core                                                                                                                                                                                                                                                                                              |

| P1  | TxData1_1   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 1                                                                                                                                                                                                                                                                                       |

|     | Priclass1_1 |                   | Priority class - most significant bit.<br>PriClass[1] is latched on reset                                                                                                                                                                                                                                            |

| N3  | TxData1_0   | I/O <sub>pu</sub> | GMII/MII transmit data - least significant bit                                                                                                                                                                                                                                                                       |

|     | PriClass1_0 |                   | Priority class - least significant bit. Sets priority level per port basis.<br>PriClass[1] - '00' - port 1 low priority<br>PriClass[1] - '01' - port 1 has normal priority<br>PriClass[1] - '10' - port 1 has high priority<br>PriClass[1] - '11' - port 1 has very high priority<br>PriClass[1] is latched on reset |

| Т3  | TxEn1       | 0                 | GMII/MII transmit enable                                                                                                                                                                                                                                                                                             |

| M3  | GTxClk1     | 0                 | GMII transmit clock                                                                                                                                                                                                                                                                                                  |

| No. | Pin label | Туре              | Description                                                                                                                                     |

|-----|-----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| P17 | Vdd 3.3   | Р                 | Digital +3.3V power supply for I/O                                                                                                              |

| T2  | TxEr1     | I/O <sub>pd</sub> | Transmit Error                                                                                                                                  |

| N2  | TxClk1    | I                 | MII transmit clock                                                                                                                              |

| J2  | Crs1      | l <sub>s</sub>    | MII carrier sense indication                                                                                                                    |

| J3  | Col1      | ls                | MII collision indication                                                                                                                        |

| N1  | RxEr1     | ls                | Receive Error                                                                                                                                   |

| L17 | Vss 3.3   | G                 | Digital ground for I/O                                                                                                                          |

| M2  | RxClk1    | I                 | MII receive clock                                                                                                                               |

| M1  | RxDv1     | I <sub>s</sub>    | GMII/MII data valid                                                                                                                             |

| J1  | RxData1_0 | I <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                               |

| K3  | RxData1_1 | I <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                               |

| K2  | RxData1_2 | I <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                               |

| M17 | Vdd 3.3   | Р                 | Digital +3.3V power supply for I/O                                                                                                              |

| K1  | RxData1_3 | I <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                               |

| L4  | RxData1_4 | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                     |

| L3  | RxData1_5 | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                     |

| L2  | RxData1_6 | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                     |

| L1  | RxData1_7 | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                     |

| U4  | selsck    | I <sub>s</sub>    | Selects the source for the system clock.<br>selsck - '1' - sysck is driven by a 25MHz external clock.                                           |

| U1  | gtxck     | I                 | The 125Mhz reference clock for 1000Mbps operating mode. This clock is used as a reference clock for the GMII transmission clock for every port. |

| V1  | Vdd 2.0   | Р                 | Digital +2.0V power supply for core                                                                                                             |

| V2  | BcstLED   | I/O <sub>pd</sub> | The led can signal filtering of broadcast frames Also the led remains lit if the POST test fails, which indicates a faulty chip.                |

| V3  | OvUnLED   | 0                 | The led is lit whenever a unicast packets overflow condition is reached and some frames are dropped by the buffer management engine.            |

| D9  | Vss 2.0   | G                 | Digital ground for core                                                                                                                         |

| U3  | sysck     | I                 | The 25MHz system clock.                                                                                                                         |

| U2  | reset     | I <sub>pus</sub>  | General reset.                                                                                                                                  |

| W9  | TxData2_7 | I/O <sub>pd</sub> | GMII transmit data - most significant bit                                                                                                       |

| Y9  | TxData2_6 | I/O <sub>pd</sub> | GMII transmit data - bit 6                                                                                                                      |

| Y8  | TxData2_5 | I/O <sub>pd</sub> | GMII transmit data - bit 5                                                                                                                      |

| W8  | TxData2_4 | I/O <sub>pd</sub> | GMII transmit data - bit 4                                                                                                                      |

| V8  | TxData2_3 | I/O <sub>pd</sub> | GMII/MII transmit data - bit 3                                                                                                                  |

|     | PriBndw1  |                   | Priority bandwidth configuration pins.<br>PriBndw(1)is latched on reset                                                                         |

| N17 | Vdd 2.0   | Р                 | Digital +2.0V power supply for core                                                                                                             |

| No. | Pin label   | Туре              | Description                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V7  | TxData2_2   | I/O <sub>pu</sub> | GMII/MII transmit data - bit 2                                                                                                                                                                                                                                                                                                         |

|     | PriBndw0    |                   | Priority bandwidth configuration pins. These configuration pins allow<br>the bandwidth percentage assigned to a priority packet queue to be<br>modified to certain hardwired levels. PriBndw chooses between 4<br>hardwired spreading percentage schemes among the 4 priority<br>queues of each port.<br>PriBndw(0)is latched on reset |

| W7  | TxData2_1   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 1<br>PriClass[2] is latched on reset                                                                                                                                                                                                                                                                      |

|     | PriClass2_1 |                   | Priority class - most significant bit.                                                                                                                                                                                                                                                                                                 |

| Y7  | TxData2_0   | I/O <sub>pu</sub> | GMII/MII transmit data - least significant bit                                                                                                                                                                                                                                                                                         |

|     | PriClass0_0 |                   | Priority class - least significant bit. Sets priority level per port basis.<br>PriClass[2] - '00' - port 2 low priority<br>PriClass[2] - '01' - port 2 has normal priority<br>PriClass[2] - '10' - port 2 has high priority<br>PriClass[2] - '11' - port 2 has very high priority<br>PriClass[2] is latched on reset                   |

| V9  | TxEn2       | 0                 | GMII/MII transmit enable                                                                                                                                                                                                                                                                                                               |

| W6  | GTxClk2     | 0                 | GMII transmit clock                                                                                                                                                                                                                                                                                                                    |

| F17 | Vss 2.0     | G                 | Digital ground for core                                                                                                                                                                                                                                                                                                                |

| Y10 | TxEr2       | I/O <sub>pd</sub> | Transmit Error                                                                                                                                                                                                                                                                                                                         |

| Y6  | TxClk2      | I                 | MII transmit clock                                                                                                                                                                                                                                                                                                                     |

| W1  | Crs2        | I <sub>s</sub>    | MII carrier sense indication                                                                                                                                                                                                                                                                                                           |

| W3  | Col2        | I <sub>s</sub>    | MII collision indication                                                                                                                                                                                                                                                                                                               |

| Y5  | RxEr2       | I <sub>s</sub>    | Receive Error                                                                                                                                                                                                                                                                                                                          |

| K17 | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                                     |

| V6  | RxClk2      | I                 | MII receive clock                                                                                                                                                                                                                                                                                                                      |

| W5  | RxDv2       | l <sub>s</sub>    | GMII/MII data valid                                                                                                                                                                                                                                                                                                                    |

| W2  | RxData2_0   | ا <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                      |

| Y1  | RxData2_1   | ا <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                      |

| Y2  | RxData2_2   | ls                | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                      |

| D16 | Vss 3.3     | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                                 |

| Y3  | RxData2_3   | l <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                      |

| V4  | RxData2_4   | ا <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                            |

| W4  | RxData2_5   | ا <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                            |

| Y4  | RxData2_6   | ا <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                            |

| V5  | RxData2_7   | ا <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                            |

| No. | Pin label   | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y17 | TxData3_7   | I/O <sub>pd</sub> | GMII transmit data - bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | EnIPPr      |                   | Enables IP prioritization. CoS resolution will consider TOS<br>Precedence bits from IP Header.<br>'1' – IP priority will be taken into consideration<br>'0' – IP priority will be neglected<br>EnIPPr is latched on reset                                                                                                                                                                                                                                                          |

| W17 | TxData3_6   | I/O <sub>pd</sub> | GMII transmit data - bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | IPTosMap1   |                   | IP type of service mapping - the most significant bit<br>IPTosMap(1) is latched on reset                                                                                                                                                                                                                                                                                                                                                                                           |

| V17 | TxData3_5   | I/O <sub>pu</sub> | GMII transmit data - bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | IPTosMap0   |                   | IP type of service mapping - the least significant bit. This configuration chooses between 4 hard-wired mapping schemes for the associations of IP priority within the received packet and one of the 4 priority levels set by PriClass.<br>In case the receiving port already has a priority level assigned by PriClass configuration, or the VLAN prioritization is also active, a resolution function is used for the final priority class.<br>IPTosMap(0) is latched on reset. |

| Y16 | TxData3_4   | I/O <sub>pu</sub> | GMII/MII transmit data - bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | EnVLANPr    |                   | Enables VLAN prioritization. CoS resolution will consider user priority<br>bits (TCI field) from 802.1Q VLAN Tag Header.<br>'1' – VLAN priority will be taken into consideration<br>'0' – VLAN priority will be neglected<br>EnVLANPr is latched on reset                                                                                                                                                                                                                          |

| W16 | TxData3_3   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | VLANPrMap1  |                   | VLAN priority mapping<br>VLANPrMap(1)is latched on reset.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| G17 | Vdd 3.3     | Р                 | Digital +3.3V power supply for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V16 | TxData3_2   | I/O <sub>pu</sub> | GMII/MII transmit data - bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | VLANPrMap0  |                   | VLAN priority mapping<br>This configuration chooses between 4 hard-wired mapping schemes<br>for the associations of VLAN priority within the received packet and<br>one of the 4 priority levels set by PriClass.<br>In case the receiving port already has a priority level assigned by<br>PriClass configuration, or the IP prioritization is also active, a<br>resolution function is used for the final priority class.<br>VLANPrMap(0)is latched on reset.                    |

| V15 | TxData3_1   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | PriClass3_1 | -                 | Priority class - most significant bit.<br>PriClass[3] is latched on reset                                                                                                                                                                                                                                                                                                                                                                                                          |

| W15 | TxData3_0   | I/O <sub>pu</sub> | GMII/MII transmit data - least significant bit                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | PriClass3_0 |                   | Priority class - least significant bit. Sets priority level per port basis.<br>PriClass[3] - '00' - port 3 low priority<br>PriClass[3] - '01' - port 3 has normal priority<br>PriClass[3] - '10' - port 3 has high priority<br>PriClass[3] - '11' - port 3 has very high priority<br>PriClass[3] is latched on reset                                                                                                                                                               |

| No. | Pin label  | Туре              | Description                                                                                                                                                                                                                                                                                                                                             |

|-----|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W18 | TxEn3      | 0                 | GMII/MII transmit enable                                                                                                                                                                                                                                                                                                                                |

| Y14 | GTxClk3    | 0                 | GMII transmit clock                                                                                                                                                                                                                                                                                                                                     |

| D15 | Vss 3.3    | G                 | Digital ground for I/O                                                                                                                                                                                                                                                                                                                                  |

| Y18 | TxEr3      | I/O <sub>pd</sub> | Transmit Error                                                                                                                                                                                                                                                                                                                                          |

| W14 | TxClk3     | I                 | MII transmit clock                                                                                                                                                                                                                                                                                                                                      |

| W10 | Crs3       | I <sub>s</sub>    | MII carrier sense indication                                                                                                                                                                                                                                                                                                                            |

| V10 | Col3       | I <sub>s</sub>    | MII collision indication                                                                                                                                                                                                                                                                                                                                |

| Y15 | RxEr3      | I <sub>s</sub>    | Receive Error                                                                                                                                                                                                                                                                                                                                           |

| H17 | Vdd 2.0    | Р                 | Digital +2.0V power supply for core                                                                                                                                                                                                                                                                                                                     |

| V14 | RxClk3     | I                 | MII receive clock                                                                                                                                                                                                                                                                                                                                       |

| Y13 | RxDv3      | I <sub>s</sub>    | GMII/MII data valid                                                                                                                                                                                                                                                                                                                                     |

| V11 | RxData3_0  | I <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                                       |

| W11 | RxData3_1  | I <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                                       |

| Y11 | RxData3_2  | I <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                                       |

| Y12 | RxData3_3  | ا <sub>s</sub>    | GMII receive data - least significant nibble.<br>MII receive data                                                                                                                                                                                                                                                                                       |

| W12 | RxData3_4  | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                                             |

| V12 | RxData3_5  | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                                             |

| V13 | RxData3_6  | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                                             |

| W13 | RxData3_7  | I <sub>s</sub>    | GMII receive data - most significant nibble                                                                                                                                                                                                                                                                                                             |

| N19 | TxData4_7  | I/O <sub>pd</sub> | GMII transmit data - bit 7                                                                                                                                                                                                                                                                                                                              |

|     | BcstThrot  |                   | Enables broadcast throttling.<br>'1' – Enable<br>'0' – Disable<br>BcstThrot is latched on reset.                                                                                                                                                                                                                                                        |

| N18 | TxData4_6  | I/O <sub>pd</sub> | GMII transmit data - bit 6                                                                                                                                                                                                                                                                                                                              |

|     | OBMTest    |                   | Sets the switch into a special test mode. This test mode require<br>crossover loopbacks cables to be placed on the pair ports: 1 & 2,2 &<br>3, 3 & 4, 4 & 5,5 & 6 while ports 0 and 7 will be accessible to the test<br>machine.<br>'1' – enabled<br>'0' – disabled<br>OBMTest is latched on reset.                                                     |

| P20 | TxData4_5  | I/O <sub>pd</sub> | GMII transmit data - bit 5                                                                                                                                                                                                                                                                                                                              |

|     | FcBcstMode |                   | <ul> <li>Changes the way flow control threshold is handled while in broadcast situations.</li> <li>'1' – only the flow control threshold on the broadcast queue is considered</li> <li>'0' – flow control thresholds associated to each source port originating the broadcast frames are considered</li> <li>FCBcstMode is latched on reset.</li> </ul> |

| No. | Pin label   | Туре              | Description                                                                                                                                                                                                                                                                                                          |

|-----|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P19 | TxData4_4   | I/O <sub>pd</sub> | GMII transmit data - bit 4                                                                                                                                                                                                                                                                                           |

|     | FcBcstEn    |                   | Enables/disables flow control for broadcast packets.<br>'1' – enabled<br>'0' – disabled<br>FcBcstEn is latched on reset.                                                                                                                                                                                             |

| P18 | TxData4_3   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 3                                                                                                                                                                                                                                                                                       |

| D17 | Vss 2.0     | G                 | Digital ground for core                                                                                                                                                                                                                                                                                              |

| R20 | TxData4_2   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 2                                                                                                                                                                                                                                                                                       |

| R19 | TxData4_1   | I/O <sub>pd</sub> | GMII/MII transmit data - bit 1                                                                                                                                                                                                                                                                                       |

|     | PriClass4_1 |                   | Priority class - most significant bit.<br>PriClass[4] is latched on reset.                                                                                                                                                                                                                                           |

| R18 | TxData4_0   | I/O <sub>pu</sub> | GMII/MII transmit data - least significant bit                                                                                                                                                                                                                                                                       |

|     | PriClass4_0 |                   | Priority class - least significant bit. Sets priority level per port basis.<br>PriClass[4] - '00' - port 4 low priority<br>PriClass[4] - '01' - port 4 has normal priority<br>PriClass[4] - '10' - port 4 has high priority<br>PriClass[4] - '11' - port 4 has very high priority<br>PriClass[4] is latched on reset |

| M18 | TxEn4       | I/O <sub>pd</sub> | GMII/MII transmit enable                                                                                                                                                                                                                                                                                             |

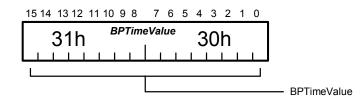

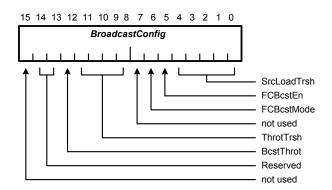

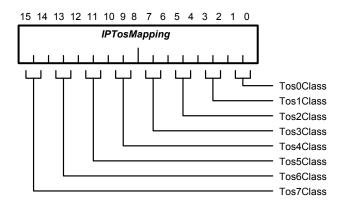

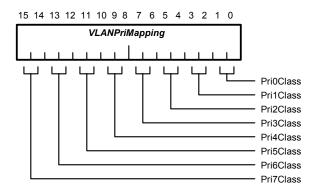

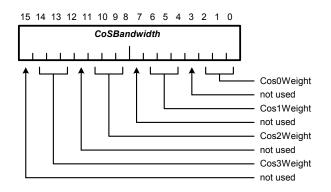

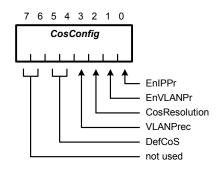

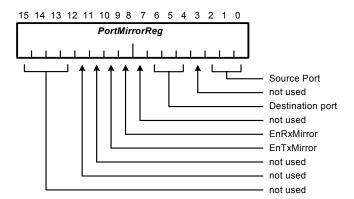

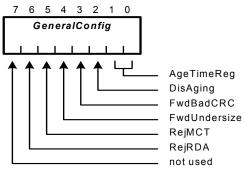

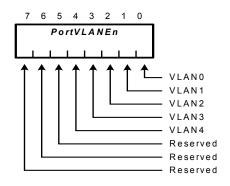

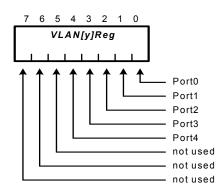

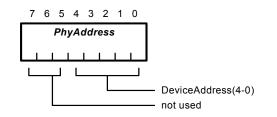

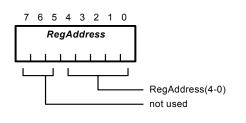

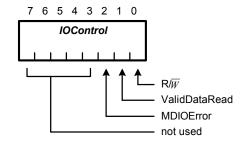

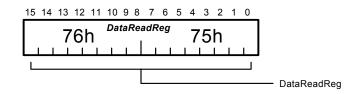

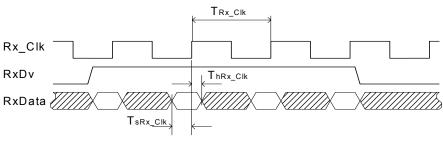

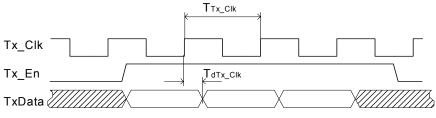

|     | RejRDA      |                   | If this pin is set to '1' then all frames with 802.1D Reserved Group<br>Address or 802.3x Full Duplex PAUSE operation DA will be filtered<br>out. This setting is provided for testing purposes only and it is<br>recommended to set high in normal operation.<br>RejRDA is latched on reset.                        |